Sep. 2021

Website: ycyk.brit.com.cn Email: ycyk704@163.com

# 微系统 Interposer 测试技术与发展趋势

秦 贺,武昊男,魏晓飞,李晓龙,冯长磊(北京微电子技术研究所,北京 100076)

摘要:随着微系统技术向三维立体集成不断发展, Interposer 技术逐渐成为关注的焦点,是未来电子系统小型化和多功能化的重要技术途径,具有广阔的应用市场和发展前景。关于 Interposer 的测试技术研究也提上发展日程。对目前 Interposer 测试技术的研究现状和发展趋势进行了综述,重点总结了研究机构在 Interposer 测试技术领域的研究现状,并对技术发展趋势做了简单展望。

关键词: 微系统; Interposer; 测试; TSV; RDL

中图分类号: TN407 文献标识码: A 文章编号: CN11-1780(2021)05-0006-07

DOI: 10.12347/j.ycyk.20210519002

引用格式: 秦贺, 武昊男, 魏晓飞, 等. 微系统 Interposer 测试技术与发展趋势[J]. 遥测遥控, 2021, 42(5): 63-69.

# Research status and development trends of Interposer test technology on micro-system

QIN He, WU Haonan, WEI Xiaofei, LI Xiaolong, FENG Changlei (Beijing Microelectronics Technology Institute, Beijing 100076, China)

**Abstract:** With the development of microsystem technology towards 3D integration, Interposer technology has become the focus of research. It is an important technology roadmap of miniaturization and multi-function of electronic systems in future, with wide market in application and prospective development. Research on the Interposer test technology is also put on the development agenda. This article gives a brief description of current status and development trend of Interposer test technology, especially focusing on the research and development by institutes. Furthermore, there is brief prospective on Interposer test technology development.

Key words: Micro-system; Interposer; Test; TSV; RDL

**DOI:** 10.12347/j.ycyk.20210519002

Citation: QIN He, WU Haonan, WEI Xiaofei, et al. Research status and development trends of Interposer test technology on micro-system[J]. Journal of Telemetry, Tracking and Command, 2021, 42(5): 63–69.

#### 引言

随着微系统技术向三维立体集成方向的不断发展, Interposer 技术逐渐成为大家关注的焦点。近 10 年来, Interposer 测试技术随着 Interposer 技术的逐渐成熟开始被广泛关注。

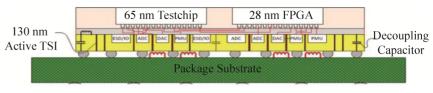

Interposer 在国内的文献中通常转译为转接板、插入层或中介层,转接板通常对应着无源 Interposer,插入层与中介层通常对应着有源 Interposer。有源与无源的最大差别在于是否基于硅基的 Interposer 实现了有源区,并以此来实现一定的系统功能<sup>[1,2]</sup>。如图 1 所示,在这个 130 nm 的有源垂直硅基插入层 ATSI(Active Through Si Interposer)上实现了 ADC、DAC、PMU 等多种功能,而图 2 的无源 Interposer 仅具备硅通孔 TSV(Through Si Via)与再布线层 RDL(Redistribution Layer)。针对上述情况,Interposer 的测试就区分为有源 Interposer 测试与无源 Interposer 测试两种。同时,根据芯片组装到 Interposer 上这个工艺过程区分为 pre-bond、mid-bond、post-bond 测试,国内文献转译为绑定前、绑定中与绑定后测试,其中,pre-bond 测试与 post-bond 测试是研究较多的两种。

\_

# 1 无源 Interposer 测试

随着对高性能、小型化与低功耗的追求不断提高,基于 TSV 等技术的三维芯片堆叠技术,也称为三维集成技术,被广泛地使用。三维集成技术使集成电路具备了

图 1 有源 Interposer 结构示意图 ig. 1 The structure of active interposer

高性能、高集成度与低功耗等优势,但同时面临着热 耗散、量产和测试成本等亟待解决的问题。

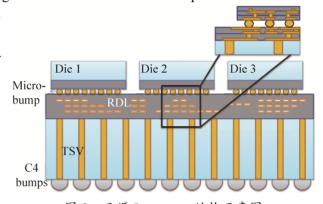

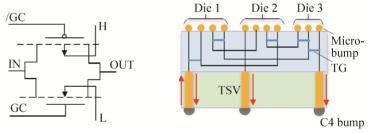

在 2.5D 集成中,裸芯通过微凸点组装到 Interposer 上。一个典型的基于无源 Interposer 的 2.5D 集成电路的横断面视图,如图 2 所示,其 Interposer 上堆叠了三颗裸芯。Interposer 包括两种类型的互联:① 由微凸点和 Interposer 顶部的 RDL 组成的水平互连,它连接各种裸芯;② 由微凸点、TSV 簇和 C4 凸点组成的垂直互联,它将裸芯连接至封装。

在 Interposer 的制造过程中, 以及在裸芯粘接和组装过程中, Interposer 互联缺陷会上升。典型的缺

图 2 无源 Interposer 结构示意图 Fig. 2 The structure of passive interposer

陷包括硬短路和开路以及导致增加互连延迟的电阻短路和电阻开路。此外,尽管互连线通常采用成熟工艺制造,但由于工艺变化<sup>[3]</sup>,互连线的实际电特性仍可能偏离其预期行为,导致小延迟缺陷。因此,有效的缺陷筛选必须作为生产过程的一部分进行。

在国内外已有很多针对无源 Interposer 测试的研究, 针对 Interposer 的组装流程, 有学者就组装前测试、组装后测试等方向也展开了讨论。

#### 1.1 无源 Interposer 组装前测试

无源 Interposer 的组装前测试,本质上是对 TSV 与 RDL 组成的传输线网络的测试,合肥工业大学 在近年针对这一方向展开研究。主要研究思路是通过设置一个辅助转接板实现对无源 Interposer 组装前 传输线网络的短路与开路故障测试<sup>[4]</sup>。

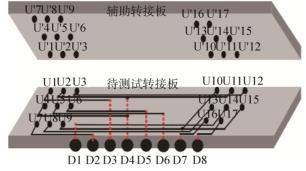

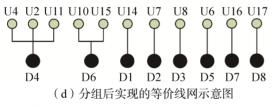

该方法使用邻接矩阵求极大独立集的方法将待测试 Interposer 上的互连线分组,并在辅助转接板上布置导线将这些互连线进行组内连接,完成短路故障测试。由于短路故障会在两个或多个线网(net)<sup>[5]</sup>之间产生一条低阻路径,因此,当两个或多个线网间存在短路故障时,对其中一个线网施加测试信号,则另外的线网将会接收到相同的信号。但直接对待测试 Interposer 进行测试仅能够完成部分线网的短路故障,因此,为了检测所有的线网间是否存在短路故障,需要通过辅助转接板实现线网补偿连接,实现对待测试 Interposer 上所有线网的短路故障测试。图 3(a)为待测试 Interposer 与辅助转接板结构示意图,图中 U 代表微凸点,D 代表 C4 凸点。图 3(b)为待测试 Interposer 上各互连线的拓扑结构图,实线表示待测试 Interposer 上的互连线。图 3(c)为分组后通过辅助转接板实现的线网,图中的虚线表示辅助转接板中布置的导线。

该方法通过在辅助转接板上布置熔丝将线网连接起来,实现开路故障测试。对互连线开路故障进行测试的原理是在互连线的一端施加测试激励,在另一端接收测试响应。同样的,直接对待测试 Interposer 进行测试仅能够完成部分线网的开路故障测试,因此,通过在辅助转接板上布置熔丝实现对辅助板上线 网的补充,实现待测试 Interposer 上所有线网的开路故障测试,并在测试完成之后熔掉熔丝,避免对后 续测试与待测试 Interposer 产生影响。图 3(d)为分组后实现的等价线网示意图。图 3(e)为设置熔丝后形成的线网示意图。

从上述方法介绍可以看出,该方法可以有效提高开路和短路故障覆盖率,但是由于引入辅助转接板, 在测试开发、测试调试等方面会增加成本。

(a) 待测试 Interposer 与辅助转接板结构示意图

(a) The schematic of the auxiliary Interposer and the Interposer under test

(b) 待测试 Interposer 上各互连线的拓扑结构图

(b) The interconnection topology of the Interposer under test

(d) The equivalent net based on the auxiliary Interposer

(c) 分组后通过辅助转接板实现的线网

( c ) The net based on the auxiliary Interposer after grouping

(e)设置熔丝后形成的线网示意图

(e) The net after setting the fuse

图 3 基于辅助转接板的无源 Interposer 测试示意图 Fig. 3 The schematic of passive Interposer test based on auxiliary Interposer

# 1.2 无源 Interposer 组装后测试

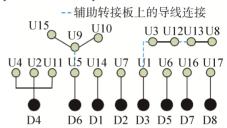

无源转接板的组装后测试,基于组装后组件上 Die 的可测性设计 DFT ( Design for Test ) 实现。美国杜克大学与高通公司联合对这一方向展开研究<sup>[2]</sup>,国内哈尔滨工业大学最近几年在这一方向上的研究初见成果<sup>[6]</sup>。针对无源 Interposer 组装后测试主要是围绕着测试结构设计展开的,主要的思路是对现有的测试标准 IEEE1149.1 进行修改,将原有的一条边界扫描链扩展至两条,通过片选可以实现原有的边界扫描工作,也可以实现测试激励移入与测试响应移出工作,解决测试数据移位过程中边界扫描链状态切换频繁导致的测试效率低等问题,同时解决原有测试标准无法满足小延迟缺陷而导致不能通过高速测试检测的问题。

这样的测试技术可以实现对 TSV、RDL 线和微凸点进行短路、开路和延迟故障检测,与 IEEE1149.1 标准完全兼容。基于对标准测试访问端口 TAP(Test Access Port)控制器的改进,该测试架构可用于高速互连测试。测试架构中提出了一种新的边界扫描结构,将扫描路径分为扫描人路径和扫描出路径,可以相互独立地并行移入测试激励和移出测试响应。

在测试过程中,扫描链用于在 Interposer 导线的一端加载激励,并在另一端捕获响应。互连测试需要两种类型的 BSC: ① 发射单元; ② 捕获单元。由于这两种类型单元在功能上是独立的,在测试过程中起着不同的作用,因此,它们的结构也不同。在测试结构设计中,边界扫描链被分成两个独立的链,即扫描输入链和扫描输出链。在扫描输入链中,所有发射单元被分组并连接在一起;同样,所有捕获单元在扫描输出链中被分组并连接在一起。这样,测试刺激的扫描输入和测试响应的扫描输出可以并行进

行,从而减少了互连测试时间。

测试架构细节如图 4 所示。芯片内部的边界扫描接口用于控制所提出的测试架构,它由四个功能元

件组成: TAP 控制器、指令寄存器、五个 TAP 引出(TCK、TMS、TRST、TDI 和 TDO)以及数据寄存器组。TAP 控制器是同步状态机(FSM),它协调数据寄存器(DR)循环和指令寄存器(IR)循环。DR 循环用于将测试信号加载到选定的数据寄存器,IR 循环用于将指令加载到指令寄存器。

为了并行地移入测试模式和移出测试响应,必须同时启用扫描输入链和扫描输出链。 因此,在 IEEE 标准边界扫描链中增加了两个额外的端口 TDI\_new 和 SO\_new。TDI\_new 连接到 Interposer 上前一个芯片的扫描输出链,SO\_new 连接到 Interposer 上后一个芯片的扫描输出链。类似地,TDI 和 TDO 分别连接到 Interposer 上的前一个和后一个裸芯的扫描输

图 4 边介扫描结构

Fig. 4 The structure of boundary scan cell

入链。在图 4 中,绿线表示扫描输入链,红线表示扫描输出链。这些链是独立的,可以同时传送信号。在 IEEE 标准边界扫描链中增加了两个复用器 M1 和 M2,用于在测试模式之间切换。

当 SIO\_select 为 1 且 BSC\_select 为 0 时,所提出的边界扫描结构被启用,测试模式的扫描输入和测试响应的扫描输出可以并行进行。当 SIO\_select 为 0 且 BSC\_select 为 1 时,启用标准边界扫描结构,用于测试 Interposer 上的芯片。

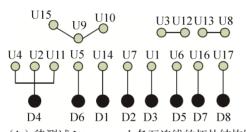

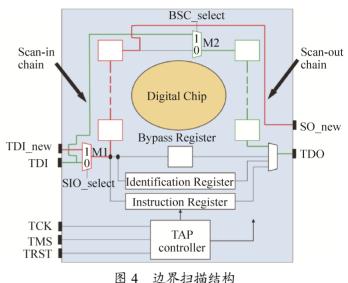

图 5 示出了不同裸芯的边界扫描链之间的连接图。有三个芯片堆叠在 Interposer 上,每个芯片都配备了本文提出的测试架构。三种测试结构都由全局端口 TCK、TMS、TRST、TDI 和 TDO 控制。由于Die1 是 Interposer 上的第一个芯片,不需要接收来自上一个扫描输出链的测试响应,因此,Die1 的 TDI和 TDI\_new 都连接到全局 TDI 端口。类似地,由于 Die3 是插入器上的最后一个芯片,并且不需要向链中的下一个扫描发送测试模式,所以使用复用器 M3 来接收来自 Die3 的 TDO 或 SO\_new 端口的信号。Die3 的输出连接到全局 TDO 端口。

图 5 边界扫描结构的互连

Fig. 5 The interconnection of boundary scan cell

从上述方法介绍可以看出,该方法可以在 Interposer 组装后,通过 Interposer 上的芯片配合互连测试

算法可以有效实现对 Interposer 的高效率、高覆盖率的故障测试,但是该方法需要依赖于 Interposer 上芯片的可测性设计实现,使得该方法的广泛应用存在一定困难。

### 2 有源 Interposer 测试

随着集成电路技术的发展,大规模芯片的良率不断下降,导致高端大规模裸芯成本增高。业界提出一种可行的解决方案:将低成品率的大规模芯片分割成更小的、成品率更好的裸芯,再通过有源 Interposer 在三维空间中制造、测试和组装形成完整的芯片<sup>[7]</sup>。专家预测有源 Interposer 将对 3D 集成电路进行优化 <sup>[8,9]</sup>。有源 Interposer 可以在实现系统集成的同时承担 ESD 保护部分,并且支持组装前测试<sup>[8]</sup>,也可以集成更多功能,如用于芯片间通信的 PHY IP、向芯片供电的嵌入式电源管理,以及 SoC 基础逻辑(时钟、测试、调试)<sup>[9]</sup>。但是为了节省成本,有源 Interposer 的逻辑密度必须保持在较低水平,以避免大规模出现 Interposer 裸片的成品率问题<sup>[7]</sup>。

对于有源 Interposer 测试,业界多数讨论也围绕输线网络的测试展开,主要原因是 Interposer 的可测性设计多数是基于系统实现的,只能在组装后实现测试。但是出于高良率的考虑,全面功能测试也可以通过晶圆级测试的方法实现。

#### 2.1 有源 Interposer 组装前测试

有源 Interposer 的组装前测试主要是围绕着有源 Interposer 上的 TSV 测试展开研究。哈尔滨工业大学在近两年对这一方向展开研究,主要思路是通过在有源区增加 CMOS 传输门将离散的互连线连接起来实现测试,这样的测试方法可以实现对所有路径的故障测试,同时不引入额外的面积开销,最终测试完成后通过互补脉冲信号断开传输门,不影响系统实际的功能。该测试方法主要还是基于有源工艺实现对传输线网络的测试<sup>[6]</sup>。

该技术提出一种基于 CMOS 传输门(TG)的测试方法,采用 TG 将离散的互连线连接起来,组成一条测试通路。传输门类似于模拟开关,接通时自身电阻很小,相当于导线;断开后电阻很大,相当于开路,其结构如图 6(a)所示。传输门的开启和关闭是由两个互补的信号控制的,当进行有源 Interposer 的

互连线测试时, GC=1(/GC=0), OUT=IN, 传输门开启, 将各离散的待测互连线连接起来, 为测试信号传输提供通路; 当测试完成后集成电路正常工作时, GC=0(/GC=1),输出端 OUT 为高阻态,传输门关闭,将两互连线的信号传输切断,不会影响电路的正常功能。

每个传输门只能连接两个相邻引脚之间的互连线,图 6 (b) 所示的电路中, 3 个 Die 在测试路径中的连接顺序为 1-2-3-1-2。

- (a) CMOS 传输门结构示意图

- (b)测试结构示意图

- (a) The CMOS transmission gate

- (b) The test structure

· 67 ·

图 6 CMOS 传输门结构和测试结构示意图

Fig. 6 The CMOS transmission gate and the test structure

所有的待测互连线都可以连接起来组成一条测试路径,故障测试可以在一个测试过程内同时进行,减少测试时间。

此外,哈尔滨工业大学还提出基于环形振荡器的有源 Interposer 组装前测试<sup>[10]</sup>,基于开关电容的有源 Interposer 组装前测试<sup>[11]</sup>等测试方法。这类测试方法主要是围绕有源 Interposer 上的 TSV 测试展开研究,通过对 TSV 传输特性或寄生参数的测试,实现有源 Interposer 测试。这类测试方法对于 TSV 的性能验证具有意义,但尚不具备广泛应用于微系统产品的批量生产测试的条件。

#### 2.2 有源 Interposer 组装后测试

有源插入层的组装后测试,主要是利用 Interposer 有源区实现可测性设计,多数情况下这一部分可测性设计可以与裸芯可测性设计配合,共同实现 Interposer 测试。同时,由于 Interposer 的可测性设计也支持裸芯的测试和集成电路的测试,法国的 CEA-Leti 研究中心与 Mentor 在 2016 年提出一种用于有源

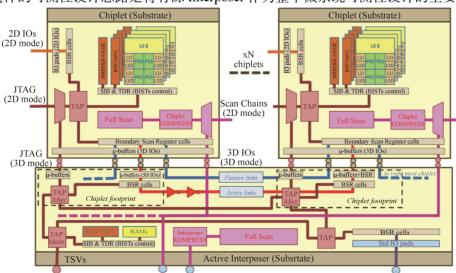

Interposer 的体系结构<sup>[7]</sup>, 定义了具备有源 Interposer 的 3D 电路应该具备的可测性设计, 并讨论了基于可测性设计可以实现的测试。

基于 IEEE 1687 和 IEEE 1149 标准来保障单颗芯片原有的边界扫描测试以及 Interposer 上的链路测试,基于全扫描测试来保障芯片结构性功能性测试,并在 Interposer 上实现全扫描测试;此外,Interposer 上的 RAM 也为其设置了内建自测试。上述这些测试在 Interposer 上由主 TAP 控制,实现对整体三维电路测试。这一部分研究与近两年发布的 IEEE 1838 标准——三维堆叠集成电路的测试访问架构(Test Access Architecture for 3D Stacked IC)[12]方向相同。

一般的有源 Interposer 体系结构包括可测性设计、测试方法等内容,通用于三维集成电路,并且与有源 Interposer 本身的系统功能无关。例如,有源 Interposer 架构可由以下单元组成:

处理元件(PEs);

由嵌入式 SRAM 组成的各级高速缓存:

各种 PAD:外部 IO 单元(2Dpad)或微缓冲单元,其两个芯片(3Dpad)之间的逻辑 3D 接口;

3D 通信链路:短距离芯片到芯片通信链路的无源链路(蓝色链路),或流水线长距离芯片到芯片通信链路的有源链路(红色链路)。

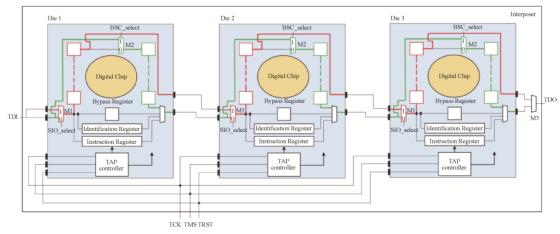

在这样的 3D 架构下,整个 3D 系统的测试必须解决以下元素的测试:标准逻辑、内存和各种 3D 互连——有源链路的 3D 连接、无源链路的 3D 连接以及常规的 2DIO 单元。为了测试有源 Interposer 及其相关芯片,所提议的测试架构的 3D 设计(图 5)基于以下两个主要的测试访问机制(TAM):

- ① 一个由 JTAG TAP 端口访问的 IJTAG IEEE 1687 分层次可配置链。

- ② 使用压缩逻辑的全扫描逻辑网络。

JTAG 链是层次化的且完全可配置的,提供对任何嵌入式测试引擎的动态访问。有源 Interposer JTAG 链的设计类似于 PCB 板上的 TAP 链,它提供了对上述三维堆叠芯片与临近芯片之间的访问。Interposer 和芯片的 JTAG 端口可在两种模式下访问:2D 模式用于组装前测试,3D 模式用于组装后测试。全扫描逻辑网络为整个三维系统逻辑提供了高效、并行的全扫描测试。同时,在扫描设计过程中融入压缩逻辑,减少 3D 并行端口的数量。

如图 7 所示,如果相同的芯片被三维堆叠到有源 Interposer 上,则可以共享芯片扫描输入端口,并行完成所有芯片的扫描输入。这类测试方法与 2.2 小节无源 Interposer 组装后测试相似,同样需要在设计阶段同步考虑芯片可测性设计对 Interposer 测试的支撑与 Interposer 可测性设计对芯片测试的支撑。由此可以看出,这样的可测性设计思路是将有源 Interposer 作为整个微系统可测性设计的主要控制部分。

图 7 用于有源 Interposer 系统的 3D-DFT 体系结构 Fig. 7 3D-DFT structure of active Interposer

# 3 Interposer 测试未来发展趋势与挑战

Interposer 技术在微电子技术迅速发展过程中,由于集成电路与微系统的高性能、小型化、异质集成、结构多样化以及成本需求,必然会从无源 Interposer 逐步向有源 Interposer 发展。未来有源 Interposer 将成为微系统产品中不可或缺的一部分。由于有源 Interposer 本身既承担着系统互联与部分系统功能的任务,又承担着系统可测性设计的主控任务,因此,有源 Interposer 的良率将成为未来微系统产品成本与良率的瓶颈之一,有源 Interposer 测试技术将成为未来微系统测试技术的重点研究内容。

目前业界对于 Interposer 测试技术的讨论可以大体分为两类: 一类是基于 TSV 特性测试的 Interposer 测试,一类是基于可测性设计的 Interposer 测试。前者更适用于 Interposer 的工艺验证,后者则具备广泛应用于微系统产品的条件。但是基于可测性设计的 Interposer 测试需要面临众多的挑战,它需要突破芯片与 Interposer 可测性设计协同设计、协同测试向量生成以及三维测试系统等一系列技术,而这些技术都需要结合微系统集成的各项技术的发展而进一步开展深入、全面的研究,才能够进一步为微系统产品测试提供有力的支撑与保证。

# 4 结束语

Interposer 技术是一项先进的系统集成技术,满足了当今电子系统高性能、小型化的发展需求,具有广阔的应用市场和发展前景。目前,Interposer 测试技术已经在业界被广泛研究,各种测试方法被提出、仿真与验证,已经成为一种人们关注和发展迅速的技术,也必将迎来广阔的发展空间,有力地支撑电子技术发展。

# 参考文献

- [1] JAVABALAN J, CHIDAMBARAM V, PEISIANG S, et al. Active through-silicon interposer based 2.5D IC design, fabrication, assembly and test[C]//IEEE 69th Electronic Components and Technology Conference(ECTC), 2019: 587–593.

- [2] WANG R, CHAKRABARTY K, BHAWMIK S. Interconnect testing and test-path scheduling for interposer-based 2.5-D ICs[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2015, (34)1: 136–149.

- [3] MARINISSEN E. Challenges and emerging solutions in testing TSV-based 2.5D- and 3D-stacked ICs[C]//Design, Automation & Test in Europe Conference & Exhibition(DATE), 2012: 1277–1282.

- [4] 刘军, 王秀云, 任福继. 使用辅助转接板和熔丝的 2.5D 集成电路测试策略[J]. 计算机工程与应用, 2020, 56(6): 271–278. LIU Jun, WANG Xiuyun, REN Fuji. Test strategy for 2.5D ICs using auxiliary interposer and E-Fuse[J]. Computer Engineering and Applications, 2020, 56(6): 271–278.

- [5] LI S M, HO C Y, GU R T, et al. A layout-aware test methodology for silicon interposer in system-in-a-package[C]// Proceedings of the Asian Test Symposium, 2013: 159–164.

- [6] 孙宁. 2.5D 集成电路测试结构设计方法研究[D]. 哈尔滨: 哈尔滨工业大学, 2019.

- [7] DURUPT J, VIVET P, SCHLOEFFEL J. IJTAG supported 3D DFT using chiplet-footprints for testing multi-chips active interposer system[C]//21st IEEE European Test Symposium(ETS), 2016.

- [8] HELLINGS G, SCHOLZ M, DETALLE M, et al. Active-Lite Interposer for 2.5 & 3D Integration[C]// 2015 Symposium on VLSI Technology, 2015.

- [9] CHERAMY S. The "active-interposer" concept for high performance chip-to-chip connections[J]. Chip Scale Review, 2014.

- [10] 徐康康. 基于环形振荡器的硅通孔测试方法研究[D]. 哈尔滨: 哈尔滨工业大学, 2019.

- [11] 方旭. 三维集成电路中 TSV 测试与故障诊断方法研究[D]. 哈尔滨: 哈尔滨工业大学, 2019.

- [12] IEEE Computer Society. IEEE 1838-2019-IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits[S/OL]. https://standards.ieee.org/standard/1838-2019.html.

#### [作者简介]

- 秦 贺 1993 年生,硕士,工程师,主要研究方向为微系统测试与验证。

- 武昊男 1993年生,硕士,工程师,主要研究方向为微系统测试与验证。

- 魏晓飞 1993 年生,硕士,工程师,主要研究方向为微系统测试与可靠性研究。

- 李晓龙 1996年生,硕士,助理工程师,主要研究方向为 DSP 嵌入式软件开发和工控软件设计。

- 冯长磊 1984年生,硕士,高级工程师,主要研究方向为微系统架构设计。