Website: ycyk.brit.com.cn Email: ycyk704@163.com

# 高速 1553B 智能通用总线测试平台设计

施 睿, 庄传刚, 张 晋, 李 霄, 刘宇航(中国运载火箭技术研究院空间物理重点实验室 北京 100076)

摘要:传统的1 Mbps 1553B 由于总线带宽受限,在航天测量控制领域正逐步被4 Mbps 高速 1553B 总线替代。一般的高速 1553B 总线测试仪不具备精准时序控制、动态消息插入和系统故障恢复的功能,难以模拟系统实际工况。因此,通过各模式下总线的初始化配置和数据收发控制,采用 SDRAM 动态读取和硬件定时触发技术,结合基于心跳和消息监测的冗余总线控制机制,设计了一种高速 1553B 智能通用总线测试平台。通过调整消息长度、消息内容和消息间隔,验证了总线测试平台 BC-RT、RT-BC、RT-RT 以及 MT 监视功能的正确性,满足了精准时序控制、动态消息插入和系统故障恢复的需求。本平台可用于半实物仿真、时序功能的验证和系统真实负载状态的测试。

关键词: 高速 1553B; 硬件定时触发; 总线数据收发; SDRAM 动态读取

中图分类号: TP336 文献标识码: A 文章编号: CN11-1780(2022)01-0111-08

DOI: 10.12347/j.ycyk.20210514003

引用格式: 施睿, 庄传刚, 张晋, 等. 高速 1553B 智能通用总线测试平台设计[J]. 遥测遥控, 2022, 43(1): 111-118.

## Design of high speed 1553B intelligent universal bus test platform

SHI Rui, ZHUANG Chuangang, ZHANG Jin, LI Xiao, LIU Yuhang

( Key Laboratory of Science and Technology on Space Physics, China Acadmey of Launch

Vehicle Technology, Beijing 100076, China )

Abstract: The bandwidth of traditional 1 Mbps 1553B bus is limited, so it is gradually replaced by 4 Mbps high-speed 1553B bus in the field of aerospace measurement and control. While the general high-speed 1553B bus tester does not have the functions of precise timing control, dynamic message insertion and system fault recovery, so it is difficult to simulate the actual working condition of the system. Therefore, a high-speed 1553B intelligent universal bus test platform is designed by using the bus initialization configuration and data transmit-receive control in each mode, SDRAM dynamic reading and writing, hardware timing trigger technology, as well as the redundant bus control mechanism based on heartbeat and message monitoring. By adjusting message length, message content and message interval, the correctness of the bus test platform functions including BC-RT, RT-BC, RT-BC and MT monitoring is verified, which meets the requirements of precise timing control, dynamic message insertion and system fault recovery. The platform can be used for hardware in the loop simulation, timing function verification and real system load status test.

**Key words:** High-speed 1553B Bus; Hardware timing trigger; Bus data transmit-receive; SDRAM dynamic reading and writing **DOI:** 10.12347/j.ycyk.20210514003

Citation: SHI Rui, ZHUANG Chuangang, ZHANG Jin, et al. Design of high speed 1553B intelligent universal bus test platform[J]. Journal of Telemetry, Tracking and Command, 2022, 43(1): 111–118.

#### 引言

MIL-STD-1553B 凭借网络结构简单、实时性好、可靠性高、易于扩展等优点,广泛应用于航空电子、航天控制测量领域。随着交互信息量的增大和实时性需求的提高,电子系统对总线速率的要求越来越高,传统 1553B 总线 1 Mbps 的传输速率在多种场合下已经捉襟见肘。随着 4 Mbps 1553B 总线控制器的使用,兼容传统传输协议的 4 Mbps 高速 1553B 通信在航天系统中逐渐获得了广泛应用。

航天测量控制系统中高速 1553B 总线具有精准时序控制、动态消息插入、系统故障恢复等功能,满

足全流程完整数据监视的需求。一般的高速 1553B 总线测试仪虽然能实现测试流程的调配和总线网络测试的自动控制,但不具备精准时序控制和动态消息插入的功能,难以模拟系统故障恢复等实际工况<sup>[1]</sup>。因此,采用 SDRAM 动态读写技术和硬件定时触发机制,结合各模式下总线的初始化配置和数据收发控制,设计一种高速 1553B 智能通用总线测试平台,用于半实物仿真、时序功能验证和系统真实负载状态的测试。

本平台可实现双通道 4 Mbps 1553B 总线通信,可实现如下具体功能:

- ① 通过 CPCI 实现与上位机的交互,实现 1553B 通信的模式选择、参数配置、消息设置或消息存储,支持 Target 和 DMA 模式,可实现 CPU 对 CPCI 设备的访问以及 CPCI 与主存之间的直接通信。

- ② BC 模式下支持自动重试和帧自动重发,支持内部触发 1 μs~65.5 ms 消息间隔设置和 100 μs~6.55 s 帧间隔设置,支持外部触发消息定时发送和消息插入。

- ③ RT模式下支持循环缓冲数据存储模式,支持循环缓冲区大小扩展,支持 RT 地址设置。

- ④ MT 模式下支持消息监视模式和 RT/消息监视组合模式 (RT/MT),支持 100%全监听总线消息,支持命令字过滤,支持完整的 RT 操作功能和其他 30 个非广播模式 RT 地址总线的监测。

- ⑤ 当 MT 模式监听到 BC 故障时,可作为备份 BC 重新配置为 BC 模式,实现系统故障的恢复。

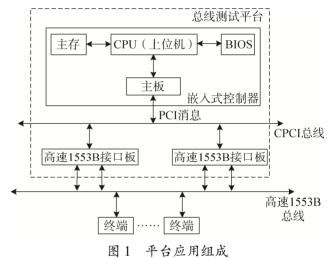

## 1 平台硬件设计

基于高速 1553B 的智能通用总线测试平台与其他终端搭配实现仿真、验证和测试功能。平台包括 CPCI 机箱、嵌入式控制器以及两块高速1553B 接口板,嵌入式控制器中 CPU 实现 X86架构的计算机功能,主板实现外设接口扩展和CPCI 链路扩展功能,主存作为计算机的缓存在DMA模式下可与 CPCI 直接通信,如图 1 所示,单块高速 1553B 接口板采用两路 LHB155304 高速 1553B 总线控制器(两路可分别实现 BC/MT、RT/RT、RT/MT 等模式)实现 MIL-STD-1553B协议。总线控制器采用抗干扰性强的 16 bits 缓冲非零等待模式,提供内置的 16 kB×16 bits 的存储单

元,外部输入时钟为 16 MHz,内部可四倍频为 64 MHz 时钟 <sup>[2]</sup>。采用隔离变压器 LS3067-3 实现终端与总线之间的短路保护、直流隔离、阻抗匹配和电平转换。当连续突发数据量较大时,芯片内置存储单元不足以缓存全部数据,考虑到LHB155304 不支持透明模式,故采用容量为 16 MB×16 bits的 SDRAM作为发送与接收缓

Fig. 1 Platform application composition

图 2 高速 1553B 接口板原理图

Fig. 2 Schematic diagram of high speed 1553B interface board

存,以较高的读写速率连续突发读写 32 MB 数据。采用 PCI 总线桥芯片 PCI9054 实现 CPCI 与 FPGA 的连接,通过外接 EEPROM 存储 PCI9054 配置信息,支持 Target 模式和 DMA 模式,便于实现各种场景下的 CPCI 主被动通信。板卡的逻辑控制由 FPGA 完成,系统供电通过 CPCI 总线和 LDO 实现。为适应 PCI 接口 33 MHz 时钟的要求,兼顾其他功能的时钟需求,FPGA 以 33 MHz 时钟为基准时钟,如图 2 所示。

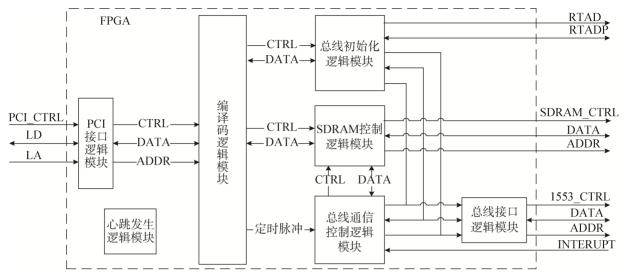

#### 高速 1553B 接口板总体逻辑设计

总体逻辑在 FPGA 上实现, 总体逻辑设计如图 3 所示:

总体逻辑框图 图 3

Fig. 3 General logic block diagram

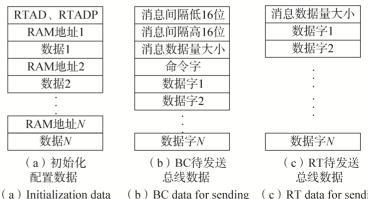

① PCI 接口逻辑模块实现 CPCI 总线对本地 RAM 和 I/O 数据的读写。上位机发送的数据主要包括 初始化配置数据、BC 待发送总线数据和 RT 待发送总线数据,为便于逻辑区分和处理,对上述三种数 据采用不同的标志区分并采用表 1 和图 4 所示数据包格式。

表 1 三种数据帧

Table 1 Three kinds of data frames

| 数据类型       | 帧标志(2B) | 字数(2B) | 有效数据区    | 校验码(2B) |

|------------|---------|--------|----------|---------|

| 初始化配置数据    | 5A52    | /      | 见图 4 (a) | CRC 校验  |

| BC 待发送总线数据 | 5A54    | /      | 见图 4 (b) | CRC 校验  |

| RT 待发送总线数据 | 5A56    | /      | 见图 4 (c) | CRC 校验  |

② 编译码逻辑模块完成上位机 指令和数据的 PCI 译码与总线接收数 据的 PCI 编码,是 PCI 接口逻辑模块 与总线初始化逻辑模块、SDRAM 控 制逻辑模块、总线通信控制逻辑模块 的桥梁。本模块的重要功能之一就是 在 BC 模式下从图 4(b) 所示的数据 帧中提取时间间隔信息, 并据此向总 线通信控制逻辑模块发送定时脉冲, 以保证总线通信控制逻辑模块定时 读取 SDRAM 中的数据。

(b) BC data for sending (c) RT data for sending

图 4 有效数据区格式

Fig. 4 Format of valid data area ③ 总线初始化模块根据上位机

发送的初始化配置数据, 在总线接口逻辑模块的配合下通过对总线控制器特定寄存器和存储空间的配置 实现 BC、RT、MT 等模式的初始化。对于 BC 模式,通过对总线控制器相关寄存器的设置实现内部触 发 1 μs~65.5 ms 消息间隔设置实现定时发送,但该种定时模式受限于芯片本身的定时长度和存储容量。 对于 RT 模式,需根据上位机发送的初始化配置数据输出高/低电平以设置总线控制器的 RT 地址。

- ④ SDRAM 控制逻辑模块实现 SDRAM 初始化和数据读写控制,完成数据缓冲。

- ⑤ 总线通信控制逻辑模块根据总线控制器针对 BC、RT、MT等不同模式的存储管理策略,在总线接口逻辑模块的配合下,完成各模式下总线数据的收发控制。收发控制的过程中,总线通信控制逻辑模块接收编译码逻辑模块的定时脉冲,通过 SDRAM 控制逻辑模块实现动态消息插入和硬件精准定时。

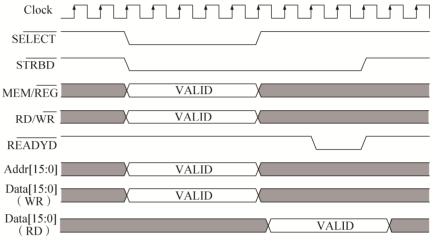

- ⑥ 总线接口逻辑模块实现总线控制器寄存器和存储空间的读写时序,时序关系如图 5 所示。在高速时钟下,FPGA 通过对 SELECT、STRBD、MEM/REG、RD/WR 的控制,完成对控制器的内部寄存器或存储器的访问。

- ⑦ 心跳发生逻辑模块产生心跳信号,用于BC与MT之间的心跳测试,相关功能将在3.4节介绍。

# 3 1553B 总线智能收发 设计

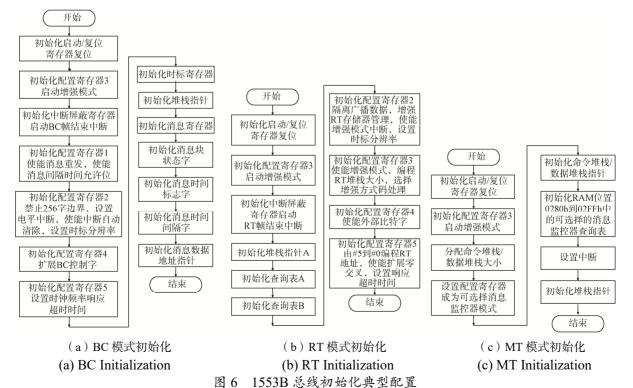

3.1 1553B 初始化典型配置 本节给出了 BC 模式、RT 模式和 MT 模式的典型初始 化配置流程。除配置基本的寄 存器外,需根据总线控制器的 存储器地址映射关系,在 BC

模式的配置过程中初始化堆

图 5 FPGA 对 1553B 控制器内部寄存器或存储器访问 FPGA access to internal register or memory of the 1553B controller

Fig. 5 FPGA access to internal register or memory of the 1553B controller

栈指针和消息计数器,在 RT 模式和 MT 模式的配置过程中初始化堆栈指针和查询表。各路 1553B 总线控制器的模式配置受上位机控制,如图 6 所示。

Fig. 6 Typical configuration of 1553B bus initialization

#### 3.2 各模式下的总线数据收发控制

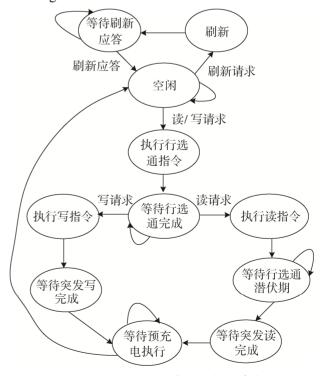

不同模式的初始化决定了总线数据收发控制的不同跳转。

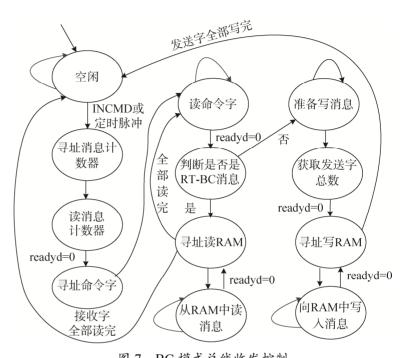

BC 模式初始化后, 总线数据收发执行 BC 模式总线收发控制逻辑: 当总线控制器 INCMD 上升沿或 定时脉冲产生时, 读取消息计数器以获取当前帧的消息数量。通过本条消息描述器堆栈的第 4 个地址空

间获取当前消息的 RAM 起始地址,进而读取命令字。若命令字表征 RT-BC 的消息,则顺序读取本消息块的消息,当接收字全部读完,开始等待下一个中断或定时脉冲。若命令字表征 BC-RT 的消息,则根据待发送字总数,在当前消息的RAM 起始地址顺序写人所有待发送字。当待发送字全部写完,开始等待下一个 INCMD 上升沿或定时脉冲。状态转换图如图 7 所示。

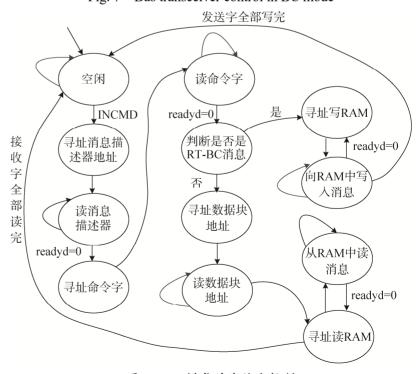

RT 模式初始化后,总线数据收发执行 RT 总线收发控制逻辑:当总线控制器 INCMD 上升沿到来时,读取消息描述器堆栈,通过本条消息描述器的第 4 个地址空间获取当前消息的命令字。若命令字表征 RT-BC 的消息,则根据待发送字总数,顺序写入所有待发送字。当待发送字全部写完,开始等待下一个 INCMD 上升沿。若命令字表征 BC-RT 的消息,则根据数据块指针获取数据块地址,顺序读取本消息块的消息,当接收字全部读完,开始等待下一个 INCMD 上升沿。状态转换图如图 8 所示。

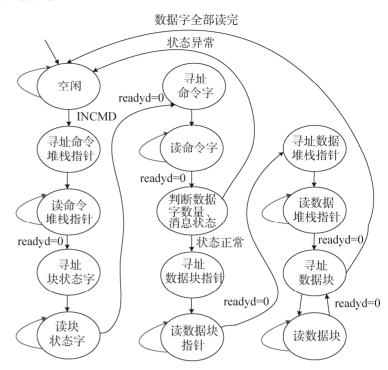

MT 模式初始化后,总线数据 监视执行 MT 总线收发控制逻辑: 当总线控制器 INCMD 上升沿到来 时,读取命令堆栈指针。根据命令 堆栈指针获取块状态字和命令字, 根据命令字获取数据字数量,根据 块状态字获取消息状态。如果消息 状态异常,则放弃该消息,等待下 一个中断;反之,则读取数据块指 针和堆栈指针,根据数据块指针和 堆栈指针,读取数据块内的数据 字。当数据字全部读完,开始等待

图 7 BC 模式总线收发控制 Fig. 7 Bus transceiver control in BC mode

图 8 RT 模式总线收发控制 Fig. 8 Bus transceiver control in RT mode

下一个 INCMD 上升沿。状态转换图如图 9 所示。

#### 3.3 动态消息插入和硬件精准定时机制

海量动态消息插入是BC或RT发送状态下的特定需求。当BC或RT待发送数据量超过总线控制器内部存储容量时,上位机将BC或RT待发送数据一次性写入SDRAM中,然后由FPGA按设定时间实现定时读取SDRAM缓存中的内容并更新RAM中消息块的命令字、数据字,进而实现大量消息的动态更新。SDRAM可通过初始化完成行选通潜伏期和突发长度的设置,然后控制数据的读写,读写逻辑状态机转换如下:

空闲状态下,如果检测到刷新请求,则执行刷新命令,等待刷新间隔计数器溢出后,收到刷新应答,回到空闲状态。如果检测到读/写请求,则执行行选通命令,待行选通命令执行完毕后,如果写请求有效则执行读命令。执行写命令时同步启动写完后自动预充,然后完成突发写,并等待预充电执行;执行读命令时同步启动读完后自动预充,等待行选通潜伏期后,才能开始突发读。完成突发读后,等待预充电执行<sup>[3]</sup>。

SDRAM 需定时刷新,刷新命令不能控制刷新的行地址,行地址由 SDRAM内部给出,内部自动累加。由于任意一行两次刷新间隔不能超过 64 ms,因此采用定时等间隔刷新,保证每 64 ms 执行一次刷新命令。每个刷新命令需要特定的执行时间,刷新命令执行时所有的 bank必须是空闲的。另外,如果刷新请求在数据读/写期间提出,则必然会导致对其响应的延迟。为解决响应延迟的问题,在计算刷新间隔时预留一个读/写操作的时间余量。

对于 BC 而言,超过 1μs~65.5 ms 范围的消息间隔须由外部硬件定时实现,可通过获取来自上位机的 PCI 消息间隔

图 9 MT 模式总线收发控制

Fig. 9 Bus transceiver control in MT mode

图 10 SDRAM 的读写逻辑状态机

Fig. 10 Reading and writing logic state machine of SDRAM

参数实现消息的定时读取。如前节图 4(b) 所述待发送总线数据的有效数据区前两个字表示本次消息与下一次消息之间的间隔,第三个字表示本消息的数据量大小,第四个字是消息命令字,若为接收数据命

令字则其后无数据字,若为发送数据命令字则后面紧跟相应数量的数据字。在 BC 非重发模式下,FPGA 将需要发送的数据依次写入到缓存 SDRAM 中,并根据数据帧中要求的时间间隔定时从缓存中读取待发送的数据并写入总线控制器;为保证数据传输和定时的可靠性,采用 FPGA 精准定时。BC 重发模式下,总线通信控制逻辑模块不读取消息间隔。

#### 3.4 基于心跳和消息监测的冗余总线控制机制

MT 作为备份 BC 时,与 BC 间通过 FPGA 心跳发生逻辑模块产生定时信号以建立心跳通信,BC 以 5 ms 定时将心跳信号传递给 MT。当 MT 总线监听到 BC 的状态故障或连续 10 ms 内未接收到 BC 的心跳信号时,则重新初始化为 BC 模式并接管总线控制权。由于 BC 和 MT 共享同一块高速 1553B 接口板的内部资源,上位机传递给 BC 的待发送数据同样能够供 MT 使用,此方法保证了 BC 故障状态下系统功能的迅速恢复<sup>[4]</sup>。

## 4 测试与分析

针对高速 1553B 智能通用总线测试平台的各项功能进行测试。通过上位机向相应总线控制器的配置寄存器和存储空间写入数据,再从中读取数据,写入和读取的数据一致,表明寄存器读写和存储器读写功能正常。

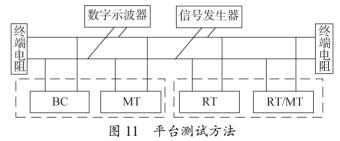

将一块高速 1553B 接口板的两路高速 1553B 总线控制器分别配置为 BC 和 MT,将另一块高速 1553B 接口板的两路高速 1553B 总线控制器分别配置为 RT/MT 模式,配备耦合器和终端电阻,利用数字示波

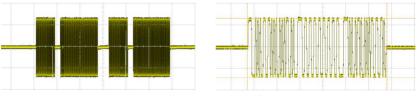

器检测 1553B 波形(包括峰峰值电压、波形上升沿/下降沿时间、终端响应时间、消息长度、消息间隔、传输速率等),用信号发生器产生频带为 1.0 kHz~8.0 MHz,有效均方根幅度为 140 mV 的高斯白噪声以检测总线的噪声抑制能力<sup>[5]</sup>,如图 11 所示。

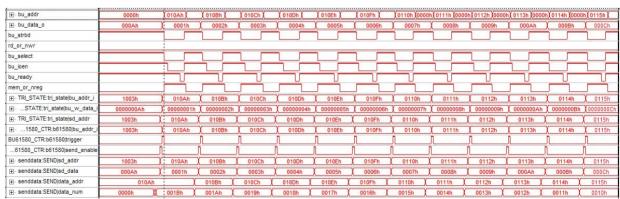

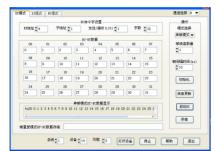

通过上位机调整 BC 的消息长度、消息内容、消息间隔以及 RT 的消息内容,检测到平台电气性能均正常,BC-RT、RT-BC、RT-RT

Fig. 11 Test method of platform

功能以及 MT 监视功能均正常,动态消息插入和硬件精准定时功能均正常。其中,FPGA 读取 SDRAM 数据并写入总线控制器的实测时序如图 12 所示,上位机交互界面如图 13 所示,利用数字示波器实测的 BC 消息波形如图 14 所示。

图 12 实测时序图

Fig. 12 Measured time sequence diagram

另外, 通过断开 BC 总线物理连接以及停止心跳信号传输的方式模拟 BC 故障, 验证 BC 故障下 MT 初始化为 BC 并接管总线控制权的功能,结果表明,该功能正常。

#### 5 结束语

本文介绍了一种高速 1553B 智能通用总线测试平台设计方案,以"4 Mbps 1553B 总线控制器+FPGA" 为核心,通过各模式下总线的初始化配置和数据收发控制,采用 SDRAM 动态读取和外部定时触发技术,结合基于心跳和消息监测的冗余总线控制机制,设计了一种高速 1553B 智能通用总线测试平台。经测试,本平台灵活可靠,能够真实模拟系统特征,提升系统测试效率,用于半实物仿真、时序功能验证和系统真实负载状态的测试,具有广阔的应用前景。

图 13 上位机交互界面

Fig. 13 Host computer interface

图 14 实测 1553B 消息波形

Fig. 14 Measured 1553B messages wave

#### 参考文献

- [1] 牛文娟, 张方, 饶张飞. 一种高速 1553B 总线控制器自动测试平台的开发[J]. 计算机测量与控制, 2020, 28(10): 7–9, 15. NIU Wenjuan, ZHANG Fang, RAO Zhangfei. Development of automatic test platform of a high-speed 1553B bus controller[J]. Computer Measurement & Control, 2020, 28(10): 7–9, 15.

- [2] 甄国涌,关瑞云,武慧军. 基于 LHB155304 的高速 1553B 总线 RT 设计与实现[J]. 实验室研究与探索, 2020, 39(7): 138–142. ZHEN Guoyong, GUAN Ruiyun, WU Huijun. Design and implementation of high speed 1553B bus RT based on LHB155304[J]. Reserch and Exploration in Laboratory, 2020, 39(7): 138–142.

- [3] 安书董, 李明, 郑久寿, 等. 一种采用可编程逻辑实现 SDRAM 的控制方法[J]. 航空计算技术, 2020, 50(4): 97–100. AN Shudong, LI Ming, ZHENG Jiushou, et al. Design of SDRAM controller based on programmable logic device[J]. Aeronautical Computing Technique, 2020, 50(4): 97–100.

- [4] 陈春燕, 杨友超, 张翔, 等. 基于 1553B 总线的飞行器电气综合系统管理设计[J]. 计算机测量与控制, 2014, 22(6): 1865–1867. CHEN Chunyan, YANG Youchao, ZHANG Xiang, et al. Design of electrical intergrated system management based on bus 1553B for aerial vehicle[J]. Computer Measurement & Control, 2014, 22(6): 1865–1867.

- [5] 范祥辉, 赵刚, 王世奎, 等. 高速 1553B 总线有效性测试平台设计与实现[J]. 现代电子技术, 2017, 40(3): 23–26. FAN Xianghui, ZHAO Gang, WANG Shikui, et al. Design and implementation of validity test platform for high-speed 1553B bus[J]. Modern Electronics Technique, 2017, 40(3): 23–26.

### [作者简介]

施 睿 1988 年生,硕士,工程师,主要研究方向为飞行器信息技术和自动测试系统。

庄传刚 1979年生,硕士,高级工程师,主要研究方向为飞行器信息技术。

张 晋 1985年生,硕士,高级工程师,主要研究方向为飞行器信息技术。

李 霄 1980 年生,博士,高级工程师,主要研究方向为飞行器信息技术。

刘宇航 1992年生,硕士,工程师,主要研究方向为飞行器信息技术。

(本文编辑:潘三英)